#### MATCHING PROPERTIES OF DEEP SUB-MICRON MOS TRANSISTORS

Jeroen A. Croon, Willy Sanser and Herman E. Maes

# MATCHING PROPERTIES OF DEEP SUB-MICRON MOS TRANSISTORS

Jeroen A. Croon, Willy Sansen and Herman E. Maes

#### MATCHING PROPERTIES OF DEEP SUB-MICRON MOS TRANSISTORS

# THE KLUWER INTERNATIONAL SERIES IN ENGINEERING AND COMPUTER SCIENCE

#### ANALOG CIRCUITS AND SIGNAL PROCESSING Consulting Editor: Mohammed Ismail. Ohio State University

#### **Related Titles:**

LNA-ESD CO-DESIGN FOR FULLY INTEGRATED CMOS WIRELESS RECEIVERS Leroux and Stevaert Vol. 843, ISBN: 1-4020-3190-4 SYSTEMATIC MODELING AND ANALYSIS OF TELECOM FRONTENDS AND THEIR BUILDING BLOCKS Vanassche, Gielen, Sansen Vol. 842, ISBN: 1-4020-3173-4 LOW-POWER DEEP SUB-MICRON CMOS LOGIC SUB-THRESHOLD CURRENT REDUCTION van der Meer, van Staveren, van Roermund Vol. 841, ISBN: 1-4020-2848-2 WIDEBAND LOW NOISE AMPLIFIERS EXPLOITING THERMAL NOISE CANCELLATION Bruccoleri, Klumperink, Nauta Vol. 840, ISBN: 1-4020-3187-4 SYSTEMATIC DESIGN OF SIGMA-DELTA ANALOG-TO-DIGITAL CONVERTERS Bajdechi and Huijsing Vol. 768, ISBN: 1-4020-7945-1 OPERATIONAL AMPLIFIER SPEED AND ACCURACY IMPROVEMENT Ivanov and Filanovsky Vol. 763, ISBN: 1-4020-7772-6 STATIC AND DYNAMIC PERFORMANCE LIMITATIONS FOR HIGH SPEED **D/A CONVERTERS** van den Bosch, Steyaert and Sansen Vol. 761, ISBN: 1-4020-7761-0 DESIGN AND ANALYSIS OF HIGH EFFICIENCY LINE DRIVERS FOR Xdsl Piessens and Stevaert Vol. 759, ISBN: 1-4020-7727-0 LOW POWER ANALOG CMOS FOR CARDIAC PACEMAKERS Silveira and Flandre Vol. 758, ISBN: 1-4020-7719-X MIXED-SIGNAL LAYOUT GENERATION CONCEPTS Lin, van Roermund, Leenaerts Vol. 751, ISBN: 1-4020-7598-7 HIGH-FREQUENCY OSCILLATOR DESIGN FOR INTEGRATED TRANSCEIVERS Van der Tang, Kasperkovitz and van Roermund Vol. 748, ISBN: 1-4020-7564-2 CMOS INTEGRATION OF ANALOG CIRCUITS FOR HIGH DATA RATE TRANSMITTERS DeRanter and Steyaert Vol. 747, ISBN: 1-4020-7545-6 SYSTEMATIC DESIGN OF ANALOG IP BLOCKS Vandenbussche and Gielen Vol. 738, ISBN: 1-4020-7471-9 SYSTEMATIC DESIGN OF ANALOG IP BLOCKS Cheung and Luong Vol. 737, ISBN: 1-4020-7466-2 LOW-VOLTAGE CMOS LOG COMPANDING ANALOG DESIGN Serra-Graells, Rueda and Huertas Vol. 733, ISBN: 1-4020-7445-X CIRCUIT DESIGN FOR WIRELESS COMMUNICATIONS Pun, Franca and Leme Vol. 728, ISBN: 1-4020-7415-8 DESIGN OF LOW-PHASE CMOS FRACTIONAL-N SYNTHESIZERS DeMuer and Steyaert Vol. 724, ISBN: 1-4020-7387-9 MODULAR LOW-POWER, HIGH SPEED CMOS ANALOG-TO-DIGITAL CONVERTER FOR EMBEDDED SYSTEMS Lin, Kemna and Hosticka Vol. 722, ISBN: 1-4020-7380-1

# MATCHING PROPERTIES OF DEEP SUB-MICRON MOS TRANSISTORS

by

#### Jeroen A. Croon

IMEC, Leuven, Belgium

#### Willy Sansen

Katholieke Universiteit Leuven, Leuven, Belgium

and

#### Herman E. Maes

IMEC and Katholieke Universiteit Leuven, Leuven, Belgium

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN 0-387-24314-3 (HB) ISBN 0-387-24313-5 (e-book)

> Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

Sold and distributed in North, Central and South America by Springer, 101 Philip Drive, Norwell, MA 02061, U.S.A.

In all other countries, sold and distributed by Springer, P.O. Box 322, 3300 AH Dordrecht, The Netherlands.

Printed on acid-free paper

All Rights Reserved © 2005 Springer

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Printed in the Netherlands.

## Contents

| Preface |                                      |                                           |                                                      |    |  |

|---------|--------------------------------------|-------------------------------------------|------------------------------------------------------|----|--|

| Ac      | Acknowledgments                      |                                           |                                                      |    |  |

| 1.      | INTRODUCTION                         |                                           |                                                      | 1  |  |

|         | 1.1                                  | Matching analysis                         |                                                      |    |  |

|         | 1.2                                  | Importance for circuit design             |                                                      |    |  |

|         | 1.3                                  | State of the art                          |                                                      |    |  |

|         | 1.4                                  | Research objectives                       |                                                      |    |  |

|         | 1.5                                  | Outlin                                    | ne of this book                                      | 8  |  |

| 2.      | MEASUREMENT AND MODELING OF MISMATCH |                                           |                                                      | 13 |  |

|         | 2.1                                  | Measu                                     | irement setup                                        | 14 |  |

|         |                                      | 2.1.1                                     | Measurement system                                   | 14 |  |

|         |                                      | 2.1.2                                     | Test structures                                      | 16 |  |

|         |                                      | 2.1.3                                     | Measurement algorithm                                | 19 |  |

|         | 2.2                                  | Experimental setup                        |                                                      |    |  |

|         | 2.3                                  | Modeling of mismatch in the drain current |                                                      | 21 |  |

|         |                                      | 2.3.1                                     | Modeling approach                                    | 22 |  |

|         |                                      | 2.3.2                                     | Impact of threshold voltage mismatch                 | 23 |  |

|         |                                      | 2.3.3                                     | Impact of current factor mismatch                    | 28 |  |

|         |                                      | 2.3.4                                     | The complete model                                   | 30 |  |

|         |                                      | 2.3.5                                     | Parameter extraction                                 | 31 |  |

|         |                                      | 2.3.6                                     | Model accuracy                                       | 35 |  |

|         | 2.4                                  | Width                                     | and length dependence                                | 35 |  |

|         |                                      | 2.4.1                                     | Width and length dependence of $\sigma_{\Delta P}^2$ | 35 |  |

|         |                                      | 2.4.2                                     | Width and length dependence of correlation           |    |  |

|         |                                      |                                           | factors                                              | 37 |  |

|    |                                      | 2.4.3  | Matching properties of a 0.18 $\mu$ m CMOS process  | 38  |  |

|----|--------------------------------------|--------|-----------------------------------------------------|-----|--|

|    | 2.5                                  | Exam   | Example: Yield of a current-steering D/A converter  |     |  |

|    |                                      | 2.5.1  | Accuracy of unit current cell based on a yield      |     |  |

|    |                                      |        | requirement                                         | 42  |  |

|    |                                      | 2.5.2  | Width and length of the unit current cell           | 42  |  |

|    | 2.6                                  | Concl  | usions                                              | 45  |  |

| 3. | PARAMETER EXTRACTION                 |        |                                                     |     |  |

|    | 3.1                                  | Extra  | traction methods                                    |     |  |

|    | 3.2                                  | Exper  | perimental setup                                    |     |  |

|    | 3.3 Comparison of extraction methods |        |                                                     |     |  |

|    |                                      | 3.3.1  | Model accuracy                                      | 53  |  |

|    |                                      | 3.3.2  | Measurement accuracy and speed                      | 55  |  |

|    |                                      | 3.3.3  | Physical meaningfulness of parameters               | 61  |  |

|    |                                      | 3.3.4  | Summary                                             | 68  |  |

|    | 3.4                                  | Future | e issues                                            | 68  |  |

|    | 3.5                                  | Concl  | usions                                              | 70  |  |

| 4. | PH                                   | YSICAI | L ORIGINS OF MOSFET MISMATCH                        | 73  |  |

|    | 4.1                                  | Basic  | operation of the MOS transistor                     | 74  |  |

|    |                                      | 4.1.1  | Regions of operation and current expressions        | 74  |  |

|    |                                      | 4.1.2  | Short- and narrow-channel effects                   | 80  |  |

|    |                                      | 4.1.3  | Gate depletion                                      | 85  |  |

|    |                                      | 4.1.4  | Quantummechanical effects                           | 85  |  |

|    |                                      | 4.1.5  | Low field mobility                                  | 86  |  |

|    | 4.2 Mismatch in the drain current    |        | atch in the drain current                           | 88  |  |

|    |                                      | 4.2.1  | Solution of the current equation in weak inversion  | 89  |  |

|    |                                      | 4.2.2  | Solution of the current equation in strong          |     |  |

|    |                                      |        | inversion                                           | 94  |  |

|    |                                      | 4.2.3  | Short- and narrow-channel effects                   | 98  |  |

|    |                                      | 4.2.4  | Comparison of mismatch in weak and strong inversion | 101 |  |

|    |                                      | 4.2.5  | Asymmetry of MOSFET mismatch                        | 105 |  |

|    | 4.3                                  | Physic | cal origins of fluctuations                         | 107 |  |

|    | -                                    | 4.3.1  | Doping fluctuations                                 | 108 |  |

|    |                                      | 4.3.2  | Impact of fluctuations in channel doping on         |     |  |

|    |                                      |        | threshold voltage                                   | 109 |  |

|    |                                      | 4.3.3  | Gate depletion                                      | 114 |  |

|    |                                      | 4.3.4  | Quantum<br>mechanical effects                       | 115 |  |

#### Contents

|    |                                                 | 4.3.5                                          | Mobility fluctuations                                      | 118          |  |

|----|-------------------------------------------------|------------------------------------------------|------------------------------------------------------------|--------------|--|

|    |                                                 | 4.3.6                                          | Combination of all effects and comparison with experiments | 121          |  |

|    |                                                 | 4.3.7                                          | Discussion                                                 | $121 \\ 125$ |  |

|    | 4.4                                             | Conch                                          |                                                            | 126          |  |

| 5. | TECHNOLOGICAL ASPECTS                           |                                                |                                                            | 129          |  |

| 0. | 5.1                                             |                                                | ology descriptions                                         | 130          |  |

|    | 5.2                                             |                                                |                                                            |              |  |

|    | 0.2                                             | 5.2.1                                          | Amorphous or poly-crystalline silicon as gate material?    | 133<br>133   |  |

|    |                                                 | 5.2.2                                          | Impact of the gate doping                                  | 136          |  |

|    | 5.3                                             | Impac                                          | t of the halo implantation                                 | 138          |  |

|    |                                                 | 5.3.1                                          | Long- and wide-channel transistors                         | 140          |  |

|    |                                                 | 5.3.2                                          | Short- and narrow-channel effects                          | 143          |  |

|    | 5.4                                             | Comparison of different CMOS technologies 1    |                                                            |              |  |

|    | 5.5                                             | Alternative device concepts 14                 |                                                            |              |  |

|    | 5.6                                             | Conclu                                         | usions                                                     | 150          |  |

| 6. | IMPACT OF LINE-EDGE ROUGHNESS                   |                                                |                                                            | 153          |  |

|    | 6.1                                             | Chara                                          | cterization of line-edge roughness                         | 154          |  |

|    | 6.2 Modeling the impact of line-width roughness |                                                | ing the impact of line-width roughness                     | 157          |  |

|    |                                                 | 6.2.1                                          | Impact of line-width roughness on the threshold voltage    | 158          |  |

|    |                                                 | 6.2.2                                          | Impact of line-width roughness on the off-state current    | 160          |  |

|    |                                                 | 6.2.3                                          | Impact of line-width roughness on yield                    | 162          |  |

|    | 6.3                                             | Exper                                          | imental investigation of the impact of LWR                 | 163          |  |

|    |                                                 | 6.3.1                                          | Experimental setup                                         | 163          |  |

|    |                                                 | 6.3.2                                          | Sinusoidally-shaped gate edges                             | 164          |  |

|    |                                                 | 6.3.3                                          | Extra rough gates                                          | 168          |  |

|    |                                                 | 6.3.4                                          | Yield                                                      | 171          |  |

|    | 6.4                                             | Prediction of the impact of LWR and guidelines |                                                            | 172          |  |

|    | 6.5                                             | Conclusions                                    |                                                            |              |  |

| 7. | CONCLUSIONS, FUTURE WORK AND OUTLOOK            |                                                |                                                            |              |  |

|    | 7.1                                             | Conclusions                                    |                                                            |              |  |

|    | 7.2                                             | Future work 1                                  |                                                            |              |  |

|    | 7.3                                             | Outlook                                        |                                                            |              |  |

viii

| Appendices                   |     |  |

|------------------------------|-----|--|

| A List of symbols            | 183 |  |

| B List of acronyms           | 189 |  |

| C Publications by the author | 191 |  |

| References                   |     |  |

| About the Authors            |     |  |

## Preface

This book examines the matching properties of deep sub-micron MOS transistors. Microscopic fluctuations cause stochastic parameter fluctuations that affect the accuracy of the MOSFET. For analog circuits this determines the trade-off between speed, power, accuracy and yield. Furthermore, due to the down-scaling of device dimensions, transistor mismatch has an increasing impact on digital circuits. Good insight in the magnitude of the fluctuations and their physical origins is therefore required.

This work studies the matching properties of MOSFETs at several levels of abstraction. Firstly, a simple and physics-based model is presented that accurately describes the mismatch in de drain current for the full bias range above the threshold voltage. This facilitates accurate circuit design for deep sub-micron technologies. Secondly, the most commonly used methods to extract the matching properties of a technology are bench-marked with respect to model accuracy, measurement accuracy and speed, and physical contents of the parameters. This creates insight in which method to use in which situation and in how to treat data presented in literature. As third topic the physical origins of microscopic fluctuations and how they affect MOSFET operation are investigated. This leads to a refinement of the generally applied  $\sigma_{\Delta P} \propto 1/\sqrt{area}$  law in both weak and strong inversion. In addition, the analysis of simple transistor models highlights the physical mechanisms that dominate the fluctuations in the drain current and transconductance. The fourth topic considers the impact of process parameters on the matching properties. In accordance with literature, it is found that the granular structure of the poly-silicon gate material can play an important role. Furthermore, it is identified that the gate does not act as an ideal mask for the halo implantation, which worsens the matching properties of a technology. Also, scaling issues are briefly addressed. Finally, the impact of gate

line-edge roughness is investigated, which is considered to be one of the roadblocks to the further down-scaling of the MOS transistor. The impact of line-edge roughness on parameter fluctuations, off-state current and yield has been modeled. The effect has also been experimentally studied by intentionally increasing the roughness and by studying transistors with sinusoidally shaped gate edges. A prediction is made about the technology node at which line-edge roughness will become an issue. Summarizing, regarding the matching properties of deep sub-micron MOS transistors, this book tries to present insight in the modeling aspects, characterization aspects, the physical origins, and technological aspects, while also extensively treating one of the main future issues. This work could therefore be useful for device physicists, characterization engineers, technology designers, circuit designers, or anybody else interested in the stochastic properties of the MOSFET.

### Acknowledgments

I would like to acknowledge the following persons for their contributions to this work.

First of all I'd like to thank coauthors prof. Herman Maes and prof. Willy Sansen. In the past few years, their thorough review of my work helped to significantly increase the quality. Dr. ir. Stefaan Decoutere, who supervised this work, is greatly acknowledged for his support, guidance, and many interesting discussions.

Special thanks must go to Hans Tuinhout from Philips Research in Eindhoven. A lot of the ideas presented in this book would not have been realized without him, especially those related to the chapter on parameter extraction. Besides Hans, I'd also like to acknowledge Régis Difrenza from ST Microelectronics in Crolles, and Johan Knol and Antoine Moonen from Philips Semiconductors in Nijmegen for their contributions to this part of the work and for fruitful discussions.

I'd also like to express my gratitude to Maarten Rosmeulen. I'm still using the environment for matching analysis that he created, and a lot of the ideas regarding the description of the mismatch in the drain current originated from him.

The work on line-edge roughness would not have been possible without the help of Peter Leunissen. I greatly appreciate our discussions on the fundamental aspects of the topic, setting up the experiments and the time he spent on creating the required test structures.

I'd also like to thank all my (former) colleagues in IMEC for making it such an inspiring environment to have worked in.

I'd finally like to acknowledge my family and friends for their contributions to life after working hours.

Jeroen Croon November 2004

## Chapter 1

## INTRODUCTION

No two transistors are the same. When closely examined, differences can be observed at several levels, that, in one way or the other, are related to distance. For instance, when two 'identical' circuits are not fabricated in the same facility, they are produced by different people using different machines. This results in slightly nonidentical circuits and different circuit yields for the two different plants. In order to minimize differences, strategies like the 'copy EXACTLY! technology transfer method' of INTEL can be employed [1]. However, even within one production facility, differences between 'identical' circuits are observed. Different lots are not always processed using the same machines, while a machine itself shows a slight drift in time, which causes differences between wafers. On a single wafer, differences between dies are observed, which are called inter-die variations. These could for example be due to the fact that during processing the temperature is slightly different at the edge of a wafer than at its center.

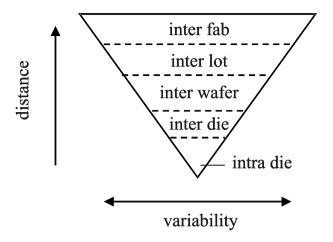

The above effects are summarized in figure 1.1. The variation between circuits increases as their distance at process time increases. At the bottom of the upturned pyramid the intra-die fluctuations are present. Intra-die fluctuations are the differences between supposedly identical structures within one die. These differences can have a systematic nature when they are caused by asymmetries in layout. For instance, it was shown in [2] that the proximity of metal wiring lines can affect transistor operation. This e.g. reduces the mirror factor of a current mirror when one of the two transistors is more closely located to the metal line, which needs to be taken into account when the circuit is designed.

Besides systematic mismatch, also a stochastic component is present

Figure 1.1. Variability at several levels

that is caused by the fact that at the microscopic level<sup>1</sup> transistors are not the same. One of the most well known examples of stochastic fluctuations in MOSFETs is the random nature of the amount of dopant atoms and their positions [3]. Stochastic fluctuations are independent of the distance between the devices under study, and by this they determine the maximal obtainable accuracy within a certain technology. In this work, we study the stochastic fluctuations of the MOSFET, which is the most important component of modern-day integrated circuits.

#### 1.1 Matching analysis

The overall variability of a component is the sum of the variabilities at all levels. When studying the stochastic component, we want to filter out all other possible causes of variation. This is achieved by matching analysis, which characterizes the difference between two devices. Consider figure 1.2, which shows two types of variation: 1) Microscopic fluctuations typically have a length scale that is shorter than the device dimensions, and can be considered as spatial noise. 2) The other types of variations have length scales that are longer. Now look at the differences between the three devices that are depicted in figure 1.2. The difference between the first and third device is for the largest part due to a disturbance close to device 3, of which the impact lessens as distance increases. In other words, because the surroundings of device 1 and device 3 are nonidentical, their behavior is also nonidentical. This is often caused by

<sup>&</sup>lt;sup>1</sup>Or at the nanoscale level for modern-day devices.